Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

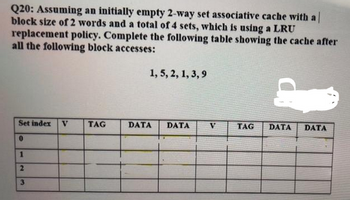

Transcribed Image Text:Q20: Assuming an initially empty 2-way set associative cache with al

block size of 2 words and a total of 4 sets, which is using a LRU

replacement policy. Complete the following table showing the cache after

all the following block accesses:

Set index V TAG

1

2

3

1, 5, 2, 1, 3, 9

DATA DATA

V

TAG DATA DATA

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 5 steps with 6 images

Knowledge Booster

Similar questions

- Caches are important to providing a high-performance memory hierarchy to processors.Below is a sequence of ten memory references in binary to an empty eight- one word blockcache. 10110,11010,10110,11010, 10000, 00011, 10000, 10010, 10000, 10111For each of these references tabulate the tag, valid bit status, the index, and the data givena direct-mapped cache. Also list if each reference is a hit or a miss, assuming the cache isinitially empty.arrow_forwardThis function will be able to look at which fields in a log entry that it needs to. When you use 64-byte cache blocks and don't prefetch, the following code calculates the average number of cache misses for each entry in the cache.arrow_forwardCaches are important to providing a high-performance memory hierarchy to processors. Below is a list of 32-bit memory address references, given as word addresses.3, 180, 43, 2, 191, 88, 190, 14, 181, 44, 186, 253For each of these references, identify the binary address, the tag, and the index given a direct-mapped cache with 16 one-word blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty.For each of these references, identify the binary address, the tag, and the index given a direct-mapped cache with two-word blocks and a total size of 8 blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty.For each of these references, identify the binary address, the tag, and the index given a direct-mapped cache with two-word blocks and a total size of 8 blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty.arrow_forward

- Using the references from Exercise 5.2, show the final cache contents for a fully associative cache with one-word blocks and a total size of 8 words. Use LRU replacement. For each reference identify the index bits, the tag bits, and if it is a hit or a miss.arrow_forwardConsider about the difference between a directly mapped cache and a totally associative cache.arrow_forwardHow does a totally associative cache function?arrow_forward

- Q20: Assuming an initially empty 2-way set associative cache with a block size of 2 words and a total of 4 sets, which is using a LRU replacement policy. Complete the following table showing the cache after all the following block accesses: Set index V TAG 1 2 3 1, 5, 2, 1, 3, 9 DATA DATA V TAG DATA DATAarrow_forwardAssume a direct-mapped cache that holds 4096 bytes, in which each block is 16 bytes.Assuming that an address is 32 bits and that cache is initially empty:a. Complete the table that follows. (You should use hexadecimal numbers for allanswers).b. Which, if any, of the addresses will cause a collision (forcing the block that was justbrought in to be overwritten) if they are accessed one right after the other? Explainarrow_forwardReplacement Policies Consider a cache using the Least Recently Used (LRU) policy with 16 blocks. If the sequence of memory block accesses is 3, 5, 2, 1, 5, 3, 4, 2, 1, what blocks will be present in the cache after these accesses?arrow_forward

- Make the difference between a cache that is directly mapped and one that is totally associative.arrow_forwardA. Does a set-associative cache need extra bits to represent how long a particular cached word has been in the cache? B. Explain why or why not? C. How is this different than set-associative and direct caches?arrow_forwardKeep in mind the difference between a fully associative cache and a directly mapped cache.arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY