Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

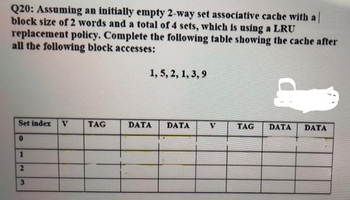

Transcribed Image Text:Q20: Assuming an initially empty 2-way set associative cache with a

block size of 2 words and a total of 4 sets, which is using a LRU

replacement policy. Complete the following table showing the cache after

all the following block accesses:

Set index V TAG

1

2

3

1, 5, 2, 1, 3, 9

DATA DATA

V

TAG DATA DATA

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 6 steps with 5 images

Knowledge Booster

Similar questions

- Consider about the difference between a directly mapped cache and a totally associative cache.arrow_forwardReplacement Policies Consider a cache using the Least Recently Used (LRU) policy with 16 blocks. If the sequence of memory block accesses is 3, 5, 2, 1, 5, 3, 4, 2, 1, what blocks will be present in the cache after these accesses?arrow_forwardIs there a way to find out which parts of a log entry a certain log processing function can read? The following code determines the typical number of cache misses per entry while using 64-byte cache blocks and no prefetching.arrow_forward

- A. Does a set-associative cache need extra bits to represent how long a particular cached word has been in the cache? B. Explain why or why not? C. How is this different than set-associative and direct caches?arrow_forwardKeep in mind the difference between a fully associative cache and a directly mapped cache.arrow_forwardMatch each type of miss with its definition. Compulsory Miss Capacity Miss Conflict Miss ✓ [Choose ] A miss that occurs because this is the first time we have accessed the block that contains the desired value A miss that occurs because the values that we are working on both map to the same place in the cache and therefore can't both A miss that occurs because we are unable to fit all of the values that we are working on inside the cache [Choose ]arrow_forward

- 3. Assuming a cache of 4096 blocks, a four-word block size, each word contains 4 bytes, and a 64-bits memory address. Memory is byte addressable, and random block replacement policy and write back policy are implemented. Find the total number of tag bits for caches that are a) direct-mapped b) 2-way set associative c) 4-way set associative d) Fully associativearrow_forwardIn a split L1 cache organization the I-cache size is 16-KB and the D-cache is 32-KB; the access time for both caches is 1 cycle. The miss rates are given in the table below. There is a 256KB second level cache (L2) that is a unified cache and has a miss rate given in the table. Please assume that miss penalty is 20 cycles to get data from L2 cache. There is a 4MB third level cache (L3) that has a latency of 42 cycles; its miss rate is 1.28%. 124 cycles are required to get data from main memory. A program executes 8.6×10° instructions; 32.8% of the executed instructions are data references (i.e. loads or stores). AMAT = Hit Time + Miss Rate x Miss Penalty Cache miss rates a) Please determine the AMAT for this memory system. [7 points] Cache Size L1 I-Cache L1 D-Cache L2 Unified Cache 8 KB 0.82% 12.21% 8.63% 16 KB 0.38% 11.36% 6.75% L1: I D 32 KB 0.14% 10.67% 5.18% 64 KB 0.06% 10.15% 4.89% L2: U_cache 128 KB 0.03% 9.81% 3.66% 256 KB 0.002% 9.06% 2.76% L3: U_cache M: Mainarrow_forwardD Question 24 Assume the address format for a 2-way set-associative cache is as follows: 4 bits 2 bits 2 bits Tag Set Offset 8 bits Given the cache directory is as shown in the diagram below, indicate which cache set the memory reference Ox5E maps to (express set number in decimal) and whether it results in a cache hits or miss Copyright © 2016-2021 by A.Berrached-All Rights Reserved. Set Tag valid 00 1 10 01 1 1 10 11 Question 25 0000 1101 0000 0001 0000 1011 0101 1000 1 1 0arrow_forward

- Asap pleasearrow_forwardQ20: Assuming an initially empty 2-way set associative cache with al block size of 2 words and a total of 4 sets, which is using a LRU replacement policy. Complete the following table showing the cache after all the following block accesses: Set index V TAG 1 2 3 1, 5, 2, 1, 3, 9 DATA DATA V TAG DATA DATAarrow_forward1. Caches are important to providing a high-performance memory hierarchy to processors. Below is a list of 32-bit memory address references, given as word addresses. 42, 137, 66, 50, 38, 225, 173, 22, 19, 88, 51, 43 a. For each of these references, identify the binary address, the tag, and the index given a direct mapped cache with 16 one-word blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty. b. For each of these references, identify the binary address, the tag, and the index given a direct mapped cache with two-word blocks and a total size of 8 blocks. Also list if each reference is a hit or a miss, assuming the cache is initially empty. Please explain the process.arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY