Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

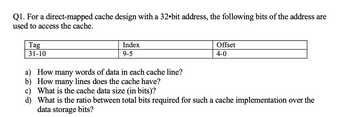

Transcribed Image Text:Q1. For a direct-mapped cache design with a 32-bit address, the following bits of the address are

used to access the cache.

Tag

31-10

Index

9-5

a) How many words of data in each cache line?

b) How many lines does the cache have?

c)

d)

Offset

4-0

What is the cache data size (in bits)?

What is the ratio between total bits required for such a cache implementation over the

data storage bits?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 2 steps

Knowledge Booster

Similar questions

- Question 1 Consider a memory system that uses a 32-bit address at the byte level, plus a cache that uses a 64-byte line size. a)Assume a direct mapped cache with a tag field in the address of 20 bits. Show the address format and determine the following parameters: number of addressable units, number of blocks in main memory, number of lines in cache, size of tag b) Assume an associative cache. Show the address format and determine the following parameters: number of addressable units, number of blocks in main memory, number of lines in cache, size of tag. c) Assume a four-way set-associative cache with a tag field in the address of 9 bits. Show the address format and determine the following parameters: number of addressable units, number of blocks in main memory, number of lines in set, number of sets in cache, number of lines in cache, size of tag.arrow_forwardQ earrow_forwardPlease explain 1,2,and 3 Consider following cache elements Cache can hold 32 kB Data are transferred between main memory and the cache in blocks of 8 bytes each Main memory consists of 256 MB For the hexadecimal main memory address 1234567, show the following information (in hexadecimal format) Tag, Line, and Offset(word) values for Direct-mapped Cache Tag and Offset(Word) values for Associative Cache Tag, Set, and Offset(word) values for aa 4-way Set-associative Cachearrow_forward

- Computer Architecturearrow_forwardSuppose a computer using direct mapped cache has 236 bytes of byte-addressable main memory and a cache size of 1024 bytes, and each cache block contains 64 bytes. ⦁ How many blocks of main memory are there? ⦁ What is the format of a memory address as seen by cache, i.e., what are the sizes of the tag, block, and offset fields? ⦁ To which cache block will the memory address 0x13A4576B map?arrow_forwardA two-way set associative cache memory uses blocks of four words. The cache canaccommodate a total of 4096 words from main memory. The main memory size is 256K x 32.a) How many bits are there in tag, index, block, and word fields of the address format.b) How many bits are there in each words of cache, and how are they divided intofunctions?c) How many blocks can the cache accommodate?arrow_forward

- Suppose a byte-addressable computer using set-associative cache has 216 bytes of main memory and a cache of 32 blocks, and each cache block contains 8 bytes.Q.) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache?arrow_forwardCA_6 We study the properties of cache memory, and for reasons of easier design and efficient circuits, we assume that the cache capacity is 2i Bytes, and cache line size is 2j Bytes, with i and j being natural numbers: (a) How many bits should the tag field have? And can the tag field contain 0 bit (i.e., be empty)? Elaborate (b) Repeat the above for the index field. (c) Repeat the above for the byte-offset field. (d) Finally, depict a figure showing a cache line, indicate what fields it possibly has, state the possible sizes of these fields, and explain the uses of these fields.arrow_forwardAssume the address format for a fully-associative cache is as follows: 6 bits 2 bits Tag Offset 8 bits Given the cache directory is as shown in the diagram below, indicate whether the memory reference Ox5E results in a cache hits or a miss. Tag valid Block 000 110110 001 000001 010 000010 011 000101 100 001000 1 101 100010 110 010111 111 110110 O Hit O Missarrow_forward

- Consider a 32-bit computer using byte-addressable memory accessing different types of cache. Each cache consists of 256 blocks with one 32-bit word per block. Specify how many bits are used for the tag, index or set, and byte offset for each type of cache listed in the table below.arrow_forwardConsider a direct-mapped cache memory with 12-bit addresses. The cache is byte-addressable. We have B = 16 bytes per block and S = 8 sets. For the address shown below. Indicate which bits correspond to the cache set index, tag bits, and block offset. Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0arrow_forwardPlease help with detailed explanation for problem C, don't copy solutions from other sources. Consider a byte addressing architecture with 64-bit memory addresses. a)Which bits of the address would be used in the tag, index and offset in a direct-mapped cache with 512 1-word blocks. b)Which bits of the address would be used in the tag, index and offset in a direct-mapped cache with 64 8-word blocks. c)What is the ratio of bits used for storing data to total bits stored in the cache in each of the above cases a and b?arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY