Database System Concepts

7th Edition

ISBN: 9780078022159

Author: Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher: McGraw-Hill Education

expand_more

expand_more

format_list_bulleted

Topic Video

Question

Transcribed Image Text:2.

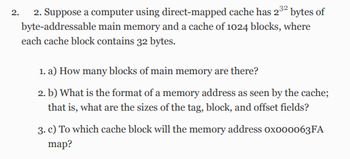

2. Suppose a computer using direct-mapped cache has 232 bytes of

byte-addressable main memory and a cache of 1024 blocks, where

each cache block contains 32 bytes.

1. a) How many blocks of main memory are there?

2. b) What is the format of a memory address as seen by the cache;

that is, what are the sizes of the tag, block, and offset fields?

3. c) To which cache block will the memory address oxoo00063FA

map?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- operating systemarrow_forward5. How many bits are required to address a 4M X 16 main memory if a) main memory is byte addressable? b) main memory is word addressable? 6. How many bits are required to address a 1M X 8 main memory if a) main memory is byte addressable? b) main memory is word addressable?arrow_forward8.9. The IBM System/370 architecture uses a two-level memory structure and refers to the two levels as segments and pages, although the segmentation approach lacks many of the features described earlier in this chapter. For the basic 370 architecture, the page size may be either 2 Kbytes or 4 Kbytes, and the segment size is fixed at either 64 Kbytes or 1 Mbyte. For the 370/XA and 370/ESA architectures, the page size is 4 Kbytes and the segment size is 1 Mbyte. Which advantages of segmentation does this scheme lack? What is the benefit of segmentation for the 370?arrow_forward

- QUESTION 9 1. If a given memory address for a byte addressable machine is found in a cache that uses a 128 byte cache line size, the least significant 8 bits in the memory address will be used to select the byte(s) in the cache line to work with. True False QUESTION 10 1. SRAM memory is used predominately in: C SRAM memory is used predominately in: C motherboard main memory C BIOS PROM memory C SD card memory devices C CPU on-chip cache memoryarrow_forward4. Assume 32 bit memory addresses, which are byte addresses. You have a direct-mapped cache with a block size of 8 bytes, and a size of 128 blocks. How many bits will the index, block offset, and tag be? How many total bits are required for the cache, including the data?arrow_forward3arrow_forward

- QUESTION 2 Suppose a computer using direct mapped cache is using 216 (64K) bytes of byte-addressable main memory, and a cache size of 4096 bytes, where each cache block contains 256 bytes. a) How many blocks of main memory are there? b) What is the format of a memory address as seen by cache, i.e. what are the length of the tag, block, and offset fields? c) Given memory address 2B9D (in hexadecimal format), which block in the cache will be searched? (What is that block's id?)arrow_forwardP2arrow_forward3. The table below represents a stack stored in a contiguous block of memory cells (as discussed in the text). If the base of the stack is at address 0x10 and the stack pointer contains the value 0x12, what value is retrieved by a pop instruction? What value is in the stack pointer after the pop operation? Address 0x10 0x11 0x12 0x13 0x14 Contents 'F' 'C' 'A' 'B' 'E'arrow_forward

- Question 9arrow_forward5. The ending address of a memory of size 1KB is 33FFH, then what is the starting address of the memory.arrow_forwardBefore we can store (save) or retrieve (load) data in and out of the main memory, we need to provide the memory address to the memory control unit. This address uniquely identifies one single location (word or record) of the memory. Suppose this address is placed in Memory Address Register (MAR) prior to each memory access. What is the size of MAR for a 4GB RAM? (RAM is byte- addressable and each word is 2 bytes). Show all the work.arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Database System Concepts

Computer Science

ISBN:9780078022159

Author:Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:9780134444321

Author:Tony Gaddis

Publisher:PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:9780132737968

Author:Thomas L. Floyd

Publisher:PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:9780133976892

Author:Paul J. Deitel, Harvey Deitel

Publisher:PEARSON

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781337627900

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education