THIS IS MY CODE SO FAR:

// header

#include <stdio.h>

// define the IM and DM size

#define IM_SIZE 250

#define DM_SIZE 10

// Define the ISA of the Tiny Machine Architecture

#define LOAD 1

#define ADD 2

#define STORE 3

#define SUB 4

#define IN 5

#define OUT 6

#define END 7

#define JMP 8

#define SKIPZ 9

// Accurately represented architecture

int PC = 0; // PC =

int IR; // IR = Instruction Register

int MAR1, MAR2; // MAR1,MAR2 = Memory Address Registers 1 and 2

int MDR1, MDR2; // MDR1,MDR2 = Memory Data Registers 1 and 2

int A = 0; // A = Accumulator

int IM[IM_SIZE]; // IM = Instruction Memory

int DM[DM_SIZE]; // DM = Data Memory

// opening the file

void openProgram(const char* filename) {

FILE* file = fopen(filename, "r");

if (file == NULL) {

printf("Error opening file.\n");

return;

}

int opcode, address;

int i = 0;

while (fscanf(file, "%d %d", &opcode, &address) == 2 && i < IM_SIZE) {

IM[i++] = opcode;

IM[i++] = address;

}

fclose(file);

}

// execute the instructions

void execute() {

int run = 1;

while (run) {

// Fetch

MAR1 = PC;

PC = PC + 2;

MDR1 = IM[MAR1];

IR = MDR1;

// use a switch to help carry out the instructions

switch (MDR1) {

case LOAD:

// LOAD

MAR2 = IR;

MDR2 = DM[MAR2];

A = MDR2;

break;

case ADD:

// ADD

MAR2 = IR;

MDR2 = DM[MAR2];

A = A + MDR2;

break;

case STORE:

// STORE

MAR2 = IR;

MDR2 = A;

DM[MAR2] = MDR2;

break;

case SUB:

// SUB

MAR2 = IR;

MDR2 = DM[MAR2];

A = A - MDR2;

break;

case IN:

// IN

printf("Input data: ");

scanf("%d", &A);

break;

case OUT:

// OUT

printf("The result is: %d\n", A);

break;

case END:

// END

run = 0;

break;

case JMP:

// JMP

PC = IR;

break;

case SKIPZ:

// SKIPZ

if (A == 0)

PC++;

break;

default:

printf("Invalid opcode encountered.\n");

run = 0;

}

// Print the current state after each instruction

printf("PC = %d | A = %d | DM = [", PC, A);

for (int i = 0; i < DM_SIZE; i++) {

printf("%d", DM[i]);

if (i < DM_SIZE - 1)

printf(", ");

}

printf("]\n");

}

printf("Program complete.\n");

}

// main method

int main(int argc, char *argv[]) {

if (argc != 2) {

printf("Usage: %s <filename>\n", argv[0]);

return 1;

}

openProgram(argv[1]);

printf("Reading Program... Program Loaded. Run.\n");

execute();

return 0;

}

the elf file:

5 5

6 7

3 0

5 5

6 7

3 1

5 5

6 7

3 2

5 5

6 7

3 3

1 0

2 2

3 0

1 3

4 1

3 3

9 0

8 12

1 0

6 7

7 0

I JUST NEED HELP FIGURING OUT HOW TO MULTIPLY THE TWO INPUT VALUES PLEASE HELP.

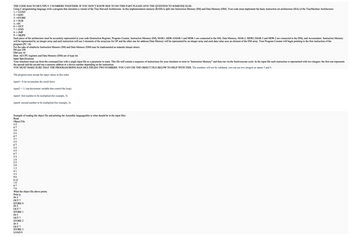

![ADD 2

STORE 0

LOAD 3

SUB 1

STORE 3

SKIP 0

JUMP 12

LOAD 0

OUT 7

END

Output Specifications

The virtual machine(VM) you are implementing should provide output according to the input file. Along with this output your program should provide status messages identifying details on the workings of your simulator. Output text does not have to reflect my example word-for-word, but please provide detail on the program

as it runs in a readable format that does not conflict with the actual output of your VM. After each instruction print the current state of the Program Counter, Accumulator, and Data Memory. The INPUT instruction is the only one that should prompt an interaction from the user.

Example:

Reading Program...

Program Loaded.

Run.

PC 10|A NULL | DM = [0, 0, 0, 0, 0, 0, 0, 0, 0, 0]

/* input value */

X

PC

12|A=X|DM = [0, 0, 0, 0, 0, 0, 0, 0, 0, 0]

/* outputting accumulator to screen */

X

PC

14|A=X | DM = [0, 0, 0, 0, 0, 0, 0, 0, 0, 0]

/* storing accumulator to memory location 0 */

PC 16|A X | DM = [X, 0, 0, 0, 0, 0, 0, 0, 0, 0]

... etc

Program complete.

Your program should compile and run from the command line with one input file parameter.

For instance, to implement FETCH and instruction LOAD you must implement each step:

FETCH

MAR1 <-PC

PC <- PC+2

MDR1 <- IM [MAR1] // IM stands for Instruction Memory (program memory)

IR <-MDR1

Case IR.OP = 1 Load is executed.

//LOAD (Execute cycle)

MAR2 <-IR.ADDR

MDR2 <- DM [MAR2] //DM stands for Data Memory

A <-MDR2

Note: you can use MAR or MAR1 for IM and MAR2 for DM.

Tiny Machine ISA:

FETCH

MARI <- PC

PC <-PC+2

MDR1 <- IM [MAR] // IM stands for Instruction Memory (program memory)

IR <-MDR1

Depending on IR.OP one of the following instructions will be executed:

(Execute cycle)

LOAD

MAR2 <- IR.ADDR

MDR2 <-DM[MAR2]

A <- MDR2

ADD

MAR2 <- IR.ADDR

MDR2 <- DM[MAR2]

A <-A+MDR2

STORE

MAR2 <- IR.ADDR

MDR2 <- A

DM[MAR2] <- MDR2

SUB

MAR2 <-IR.ADDR

MDR2 <- DM[MAR2]

A <- A - MDR2

IN

A <- Input value from keyboard (emit a message to the user: "Input data:”)

OUT

Screen <-A (emit message to the user: "The result is:"

END

Run <- 0 // In your program Run must be initialized to 1 to control the instruction cycle.

JMP

PC <- IR.ADDR

SKIP

IF (A=0) PC PC + 1|](https://content.bartleby.com/qna-images/question/44870f31-83c6-452e-ba54-77702704a3ca/ebaccba4-44b0-4645-a139-dcd87b942a76/x2rdq0c_thumbnail.png)

Step by stepSolved in 2 steps

- Full explanation of what you did please step by steparrow_forwardFor the below microprogrammed architecture, what is the ALU sequence of actions/micro instruction code: ALU(F2,F1,F0) required to implement the instruction SUB DO, D1,#1? Assume that CL1 =0 for Latch 1 and CL2 =1 for Latch 2 Note: The table below defines the effect of the ALU's function code. Bus A Bus B Guen Read Write Data out Main store TE Guow wData in The memory performs a read when Read 1 TEus Address and a write when Write = 1 Cuan MAR Curn Gvern F2 F1 FO Operatlon MBR Copy P ta bus A A=P G. Gr IR 1 Copy Q to bus A A = Q Grc Copy P+1 to bus A A =P+1 PC 1 TE Gọo Cp 1 1 Copy Q+1 to bus A A = Q+1 DO 1 Copy P- 1 to bus A A =P -1 Co Got D1 1 Copy Q - 1 to bus A A =Q 1 TEO 1 1 Copy bus P +Q to bus A A =P+Q ALU P f(PO) A =P - Q Latch 1 1 Copy bus P Q to bus A t O Latch 2 Function select F, F, Fo F2F1F0=111 O F2F1F0=100 F2F1F0=101 O F2F1F0=010arrow_forwardComputer architecturearrow_forward

- Describe the protection and instruction mechanisms of the set architecture.arrow_forwardTopic: MARIE Assembly Language (Simulator) Identification: Using MARIE Assembly Simulator, identify the following: ____________1. If the first (and current) instruction is located at address 000, what is the address of the next instruction (in hex)? _____________2. What is the opcode of the instruction in memory address 001 (in hex)? _____________3. What is the operand of the instruction in the IR? Make sure to input the complete operand in hex. _____________4. What is the address of the memory location that contains your first input value (in hex)? That is, in which address was your input value stored? _____________5. Go to Help → Instruction Set, look for the instruction that corresponds to the opcode of the instruction in memory address 000. What is the instruction in memory address 000?arrow_forwardConvert following x86-64 assembly language function into C code f2: addl %edx, %esi movslq %esi, %rsi movl (%rdi,%rsi,4), %eax retarrow_forward

- Computer Architecture Consider the below one-bus organization find the micro-operations at each step for the following instructions: 1- Instruction Load (100), R4 (R4 M[M[100]]) 2- JUMP X, where X is a memory location that contains the address of the instruction to be executedarrow_forwardBriefly state how each of the following 8051 addressing modes operate including asimple assembly language example of each: i) Direct Addressingii) Indirect Addressingiii) Indexed Addressingiv) Immediate Addressingarrow_forwardmicroprocessor 8086arrow_forward

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education