Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN: 9780133923605

Author: Robert L. Boylestad

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

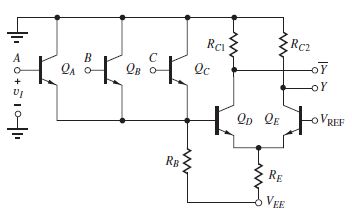

Assume that you need 0.6 V across RE to properly

stabilize the current in the modified ECL gate

as shown. Design the resistors in the gate for

a logic swing of 0.4 V and an average current of

1 mA through RB and RE . What are the minimum

values of VEE and the value of VREF?

Transcribed Image Text:Rc2

RCi

oF

Qc

oY

A

VREF

Op QE

RB

RE

VEE

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 5 steps with 9 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Similar questions

- Draw the logic diagram and logic equation of the followings: NAND IMPLEMENTATION: A. NOT B. AND C. OR D. XOR E. XNOR NOR IMPLEMENTATION: A. NOT B. AND C. OR D. XOR E. XNORarrow_forwarda) A standard TTL inverter gate is shown in the figure. The supply voltage is 5V. Calculate the output voltage for both logic low and logic high input cases assuming input voltages respectively as 0.11V and 4.2V. Br= 130; BR = 0.24. You can make approximations when needed. Br = IcIs active region; BR = IE/ls inverse active region b) Assume you connect a resistor of 1.8K to the output of the circuit when the output is at logic high. What will be the change in the output voltage? 1302 R3 1.6k2 R, 4k2 Input o T, Output T, V, V. IkQ R,arrow_forwardDesign complex CMOS logic gates.arrow_forward

- The inverter 74 ALSO4 has the following specifications IOHmax = -0.4 mA, IoLmax = 8 MA, IiHmax = 20 mA, IiLmax = -0.1 mA, Find the fan out.arrow_forwardAssume Vth = 1V and k = 50mA/V2. Given the schematic below, do the following: 1) Indicate and verify the state of each MOSFET and ?0 for the following input combinations. Fill-out the table below for each assumed state of the MOSFET for every input combination. Use ?ds,on approximation for linear operation. 2) Determine what kind of logic circuit is implemented in the circuit.arrow_forwardPlease answer the question with stepsarrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:9781337900348

Author:Stephen L. Herman

Publisher:Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:9780078028229

Author:Charles K Alexander, Matthew Sadiku

Publisher:McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:9780134746968

Author:James W. Nilsson, Susan Riedel

Publisher:PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:9780078028151

Author:Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:Mcgraw-hill Education,