Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

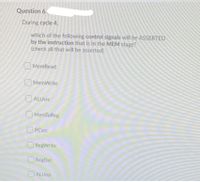

Transcribed Image Text:Question 6

During cycle 4,

which of the following control signals will be ASSERTED

by the instruction that is in the MEM stage?

(check all that will be asserted)

MemRead

O MemWrite

O ALUsrc

O MemToReg

OPCsrc

ORegWrite

ORegDst

OALUOP

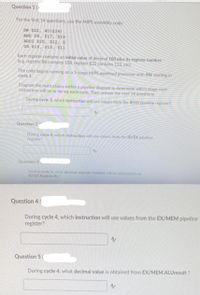

Transcribed Image Text:Question 1 (>

For the first 14 questions, use the MIPS assembly code:

SW $22, 40 ($24).

AND $8, $17, $18

ADDI $20, $12, 5

OR $16, $10, $11

Each register contains an initial value of decimal 100 plus its register number.

(e.g. register $8 contains 108, register $22 contains 122, etc).

The code begins running on a 5-stage MIPS pipelined processor with SW starting in

cycle 1.

Diagram the instructions within a pipeline diagram to determine which stage each

instruction will be in during each cycle. Then answer the next 14 questions,

During cycle 3, which instruction will use values from the IF/ID pipeline register?

Question 2

During cycle 4, which instruction will use values from the ID/EX pipeline

register?

Question 3

During cycle 4, what decimal register number will be obtained from

ID/EX.RegisterRs?

Question 4

During cycle 4, which instruction will use values from the EX/MEM pipeline

register?

Question 5 (

During cycle 4, what decimal value is obtained from EX/MEM.ALUresult ?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 2 steps with 1 images

Knowledge Booster

Similar questions

- For the following assembly code that is vaguely MIPS-like, trace its execution in both the R3000 and R4000 pipelines using a Gantt chart (or table of some kind).LOAD R1, Memory(12340)LOAD R2, Memory(12350)ADD R3, R1, R2 // R3 = R1 + R2ADD R3, R3, R3 // R3 = R3 + R3STORE R3, Memory(12360) I know other students have posted similar questions and they are answered, but those answers do not seem correct to me, so please do not copy from them.arrow_forwardWe have three 4-bit registers A, B, and C available, each with the standard "Load" input. When "Load" is at 1, then 4-bit data available on the input of a register is loaded into the register at the next rising clock edge. Assume registers A and B are already loaded with 4-bit data representing unsigned numbers. We need to design the data path for the following case: If value stored in register A is an odd number, then register C should be loaded with the sum of values present in A and B registers; else, register C should be loaded with binary value 0000. Your design may include standard logic gates, adders, and multiplexers.arrow_forwardWe have three 4-bit registers A, B, and C available, each with the standard “Load” input. When “Load” is at 1, then 4-bit data available on the input of a register is loaded into the register at the next rising clock edge. Assume registers A and B are already loaded with 4-bit data representing unsigned numbers. We need to design the data path for the following case:If value stored in register A is an odd number, then register C should be loaded with the sum of values present in A and B registers; else, register C should be loaded with binary value 0000.Your design may include standard logic gates, adders, and multiplexers. PLEASE DRAW THE DIAGRAM WITH EXPLANATIONarrow_forward

- 2. Memory contents (in hexadecimal) are 0005, 0001, 0123 for addresses 000 to 002, then 2002, 1000, 7800, F400 for addresses 80A through 80D. AC starts with value 0F24, PC has the value 80A, and AR has the value 4F5. Starting with time-step T0, describe what happens until the next TO. Make sure to indicate any updated register values as they happen. (Assume R= 0.) Refer to table 5.6 from Mano's textbook. F24 1 ARarrow_forwardI need proper explanationarrow_forwardQuestion 5 Write MIPS assembly program to print integer number from 1 to 100. Each number should be printed in a separate line. Note: • The system call code is 1 for printing an integer and is 11 for printing a character. For both cases, the argument (i.e., data to print) should be stored in $a0. • The character of "new line" is "\n. • You can use instruction li $r "\n' to load the character "\n' into a register $r. Edit View Insert Format Tools Table 12pt v Paragraph v B IUA vev T? v :arrow_forward

- 1. If the AL register is storing the binary number 10010010, what will be the contents of the BX register in binary after the instruction "movzx bx, al"? What would be the contents of the BX register in binary if this instruction is performed instead: "movsx bx, al"? What happens if you set ECX to 0 before beginning a loop? Is LOOP an unconditional or conditional transfer instruction?arrow_forwardHow many trap service routines could theoretically be created for the LC-3, given the format of the TRAP instruction? (hint: how many bits are used for the trap vector?) 8 64 O 256 О 16к 32arrow_forwardSuppose that we are developing a new version of the AMD Barcelona proces- sor with a 4 GHz clock rate. We have added some additional instructions to the instruction set in such a way that the number of instructions has been reduced by 15% from the values shown for each benchmark in Exercise 1.12. The execution times obtained are shown in the following table. a. Name Execution Time (seconds) Reference Time (seconds) bzip2 700 9650 SPECratio 13.7 1.13.2 [10] In general, these CPI values are larger than those obtained in previous exercises for the same benchmarks. This is due mainly to the clock rate used in both cases, 3 GHz and 4 GHz. Determine whether the increase in the CPI is similar to that of the clock rate. If they are dissimilar, why?arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY