Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

i need help with the step 4 part mainly. ive already done the verilog and gotten that schematic.

Transcribed Image Text:Based on Slide #27

1. From the state-assigned table, derive (backwards) the stage diagram (Moore).

2. Develop the Verilog code using the template.

3. Obtain the schematic

4. Based on the state-assigned table, derive the circuit using Boolean logic. Using Kmap and Boolean logic to get

the next state logic and the output logic. Derive the circuit with D flip-flops based on the logics you derived.

5. Compare the two schematics, and document it in a word file.

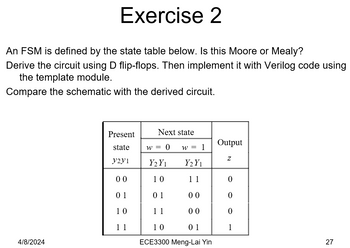

Transcribed Image Text:Exercise 2

An FSM is defined by the state table below. Is this Moore or Mealy?

Derive the circuit using D flip-flops. Then implement it with Verilog code using

the template module.

Compare the schematic with the derived circuit.

Present

Next state

state

w = 0

w = 1

Output

y2y1

Z

Y2Y1

Y2Y1

00

10

11

0

01

01

00

0

10

11

00

1

10

01

1

4/8/2024

ECE3300 Meng-Lai Yin

24

27

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 2 steps with 2 images

Knowledge Booster

Similar questions

- Answer All questions. Take screenshots when using MATLAB to write the scripts and insert them in your final report. 3. Plot a two-dimensional graph of the two vectorsx=[ 10.2 * 30 40 50 60 70 ] andy = [11 23 14 16 22 23 25] using the plot command.Add to the graph a suitable title along with labels for the x-axis and the y-axis. 4. Plot the mathematical function y = 4x ^ 2 + 3 in the range x from - 7to + 7 o Include a title for the graph as well as labels for the two axes.o Show the curve with a blue dashed line with circle symbols at the plotted points. 5. Plot the following four mathematical functions each with its own diagram using the subplot command. The functions are y = 2x ^ 3 - 4 z = x + 1 , d = x ^ 2 - 2 and v = x ^ 2 + 3 . Use the vector x=[1 2 3 4 5 6 7 8 9 10] as the range for x.o Include a title for the graph as well as labels for the two axes.o Print the legend boxo Move the legend box to the south east 6. Use the surf command to plot a three-dimensional surface of…arrow_forwardShow that you understand Cascading Style Sheets.arrow_forwardWhy we like the GUI programming component of the event delegation architecture. Do you have any examples to support your assertions?arrow_forward

- Why we prefer the GUI programming component of the event delegation architecture. Do you have any examples to support your claims?arrow_forwardHi, I'm having trouble with a particular problem and was wondering if you could help. I find that using digital visual aids, such as diagrams, really improves my understanding, as I learn best through visual representation. Specifically, I'm looking for guidance on part E of problem 1.18. I've provided details for both 1.18 part E and exercise 1.6 for your reference. Could you please walk me through the solution step by step using digital illustrations? question that I am struggling with: 1.18 Give regular expressions generating the languages of Exercise 1.6. Exercise 1.6 1.6 Give state diagrams of DFAs recognizing the following languages. In all parts, the alphabet is {0,1}. E. {w | w starts with 0 and has odd length, or starts with 1 and has even length}arrow_forwardUse a real-world class and item to demonstrate.arrow_forward

- Write down the pros and cons of using the star shape instead of the snowflake shape. Which is odder?arrow_forwardHi, could you create a state diagram for Part A? Visualizing it would really help me understand. Additionally, I'm seeking assistance with both Part A and Part B. If you could label the different sections, it would make it much easier for me to grasp. I'm really struggling with this problem and its related challenges, so your help would be greatly appreciated. Thank you.arrow_forwardCan you please explain more and the provided image is not showing as expectedarrow_forward

- Build on our PBM image creator from (code shown below) to create a fully functional image editor (in C++), using 2D arrays to store our changes. To make it more interesting by switching to the Portable Gray Map standard. 8 bit PGM files have color values ranging from 0 (black) to 255 (white), with the values in-between being shades of gray. The header is very similar to PBM, and looks like this: P2 WIDTH HEIGHT 255 IMAGE_DATA The P2 tells image readers that it is a PGM file, and the 255 indicates the largest possible color value is 255. You will first prompt the user to enter a width, height, and initial color value to fill the image. You should then create a 2D array with those dimensions and initialize each cell with that color value. You will then use a loop to create a menu that repeatedly prompts the user to make one of the following choices: Fill in a pixel with a new color ◦ Prompt the user to enter a row and column value and a new color value. If the array has that row and…arrow_forwardthe solution was not correct. I try to run it but it's not correct. My question need to provide screenshotarrow_forwardThat it allows for programming in a graphical user interface is one of the main reasons we like the event delegation framework. Is there anything I can do for you?arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY