Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

Answer last three please

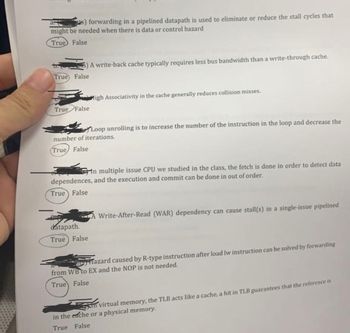

Transcribed Image Text:s) forwarding in a pipelined datapath is used to eliminate or reduce the stall cycles that

might be needed when there is data or control hazard

True False

True False

True False

A write-back cache typically requires less bus bandwidth than a write-through cache.

Migh Associativity in the cache generally reduces collision misses,

Loop unrolling is to increase the number of the instruction in the loop and decrease the

number of iterations.

True False

datapath.

True False

In multiple issue CPU we studied in the class, the fetch is done in order to detect data

dependences, and the execution and commit can be done in out of order.

True False

Write-After-Read (WAR) dependency can cause stall(s) in a single-issue pipelined

Hazard caused by R-type instruction after load lw instruction can be solved by forwarding

from WB to EX and the NOP is not needed.

True False

in virtual memory, the TLB acts like a cache, a hit in TLB guarantees that the reference is

in the eache or a physical memory.

True False

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 3 steps

Knowledge Booster

Similar questions

- For questions 10, 11, 12, in the options, there are no options in which c1=2 for ech of the questions, can you tell me correct options for 10 11 and 12?arrow_forwardcan you slove more 3 queriesarrow_forwardWhich one of the following SQL statements produces the same result asselect time_of_day_hour, time_of_day_minute, time_of_day_secondfrom time_of_daywhere time_of_day_hour BETWEEN 2 and 8; Question 1 options: 1) select time_of_day_hour, time_of_day_minute, time_of_day_secondfrom time_of_daywhere time_of_day_hour >= 2 and time_of_day_hour <= 8; 2) select time_of_day_hour, time_of_day_minute, time_of_day_secondfrom time_of_daywhere time_of_day_hour > 2 and time_of_day_hour < 8; 3) select time_of_day_hour, time_of_day_minute, time_of_day_secondfrom time_of_daywhere (2 <= time_of_day_hour <= 8); 4) select time_of_day_hour, time_of_day_minute, time_of_day_secondfrom time_of_daywhere time_of_day_hour > 2 and <8;arrow_forward

- What’s the difference between the UNION and UNION ALL set operators?arrow_forwardWhich SQL statement lists the number of employees in each department? SELECT COUNT(EmployeeID), Department FROM Employees WHERE Department; SELECT COUNT(EmployeeID), Department FROM Employees GROUP BY Department; SELECT MAX(EmployeeID), Department FROM Employees GROUP BY Department; SELECT EmployeeID, Department FROM Employees WHERE COUNT (EmployeeID) GROUP BY Department;arrow_forwardSql server 2019 Get a count of Invoices that have a Payment Total greater than $1,000.arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY