Database System Concepts

7th Edition

ISBN: 9780078022159

Author: Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher: McGraw-Hill Education

expand_more

expand_more

format_list_bulleted

Topic Video

Question

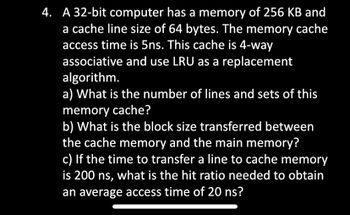

A 32-bit computer has a memory of 256 KB and a cache line size of 64 bytes. The memory cache access time is 5ns. This cache is 4-way associative and use LRU as a replacement

a) What is the number of lines and sets of this memory cache?

b) What is the block size transferred between the cache memory and the main memory?

c) If the time to transfer a line to cache memory is 200 ns, what is the hit ratio needed to obtain an average access time of 20 ns?

Transcribed Image Text:4. A 32-bit computer has a memory of 256 KB and

a cache line size of 64 bytes. The memory cache

access time is 5ns. This cache is 4-way

associative and use LRU as a replacement

algorithm.

a) What is the number of lines and sets of this

memory cache?

b) What is the block size transferred between

the cache memory and the main memory?

c) If the time to transfer a line to cache memory

is 200 ns, what is the hit ratio needed to obtain

an average access time of 20 ns?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 4 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- A memory system has 4 KB byte-addressable main memory and a direct-mapped cache that consists of 8 blocks with 16 bytes per block. The following shows the main memory address format that allows us to map addresses from main memory to cache. Note: 12 bit address, 4 bit offset, 3 bit $block, and 5 bit tag Assume the cache directory shown below:arrow_forwardSuppose a byte-addressable computer using set-associative cache has 216 bytes of main memory and a cache of 32 blocks, and each cache block contains 8 bytes.Q.) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache; that is, what are the sizes of the tag, set, and offset fields?arrow_forwardC++ Programming: How would you write a function that takes a filename and an array of struct time, opens a file, reads each line in the file as the number of days, converts this to a struct time and stores this is in an array? Here is my code so far (p.s. the function i need help with is called void readData): #include<iostream>#include<string>#include<fstream>#include<cstdlib>#include<vector> using namespace std; struct time{// private:int years, months, days;//public: time(){}time(int days){}}; time getYearsMonthsDays(int days){time x;x.years = days/450;days = days%450;x.months = days/30;x.days = days%30;return x;} int getTotalDays(time x){int totalDays;totalDays = x.years*450 + x.months*30 + x.days;return totalDays;} void openofile(string ofilename,ofstream &fout){fout.open(ofilename.c_str());if(!fout){cout << "Error opening output file..." << endl;exit(1);}} void openifile(string ifilename,ifstream…arrow_forward

- Suppose a computer using direct mapped cache has 236 bytes of byte-addressable main memory and a cache size of 1024 bytes, and each cache block contains 64 bytes. ⦁ How many blocks of main memory are there? ⦁ What is the format of a memory address as seen by cache, i.e., what are the sizes of the tag, block, and offset fields? ⦁ To which cache block will the memory address 0x13A4576B map?arrow_forwardSuppose a byte-addressable computer using set-associative cache has 216 bytes of main memory and a cache of 32 blocks, and each cache block contains 8 bytes.Q.) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache?arrow_forwardSuppose a byte-addressable computer using set associative cache has 8M byes of main memory and a cache of 128 blocks, where each cache block contains 64 bytes. a) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 16-way set associative, what is the format of a memory address as seen by the cachearrow_forward

- 5. suppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a cache of 128 blocks, where each cache block contains 64 bytes. a) how many blocks of main memory are there? b) what is the format of a memory address as seen by the cache ; that is, what are the size of the tag and offset field. c) To which cache block will the memory address 0x01D872 map?arrow_forwardComputer science homework Please help me with this homework question.arrow_forwardQuestion 4arrow_forward

- A 2-way set associative cache consists of four sets. Main memory contains 2K blocks of eight words each. Show the main memory address format that allows us to map addresses from main memory to cache. Be sure to include the fields as well as their sizes. Compute the hit ratio for a program that loops 6 times from locations 8 to 51 in main memory. You may leave the hit ratio in terms of a fraction. Please show details how you obtain the result.arrow_forward4. Suppose a computer using a fully associative cache has 2^24 byte of byte-addressable main memory and a cache of 128 blocks, where each block contains 64 bytes. a) How big in kilobytes is main memory? b) How big in bytes is cache? In kilobytes? c) How many blocks of main memory are there? d) What is the format of a memory address as seen by the cache, i.e., what are the sizes of the tag and offset fields? e) To which cache block will the memory address 0x01D8729A map?arrow_forwardQUESTION 2 Suppose a computer using direct mapped cache is using 216 (64K) bytes of byte-addressable main memory, and a cache size of 4096 bytes, where each cache block contains 256 bytes. a) How many blocks of main memory are there? b) What is the format of a memory address as seen by cache, i.e. what are the length of the tag, block, and offset fields? c) Given memory address 2B9D (in hexadecimal format), which block in the cache will be searched? (What is that block's id?)arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Database System Concepts

Computer Science

ISBN:9780078022159

Author:Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:9780134444321

Author:Tony Gaddis

Publisher:PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:9780132737968

Author:Thomas L. Floyd

Publisher:PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:9780133976892

Author:Paul J. Deitel, Harvey Deitel

Publisher:PEARSON

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781337627900

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education