Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

Please do question 4

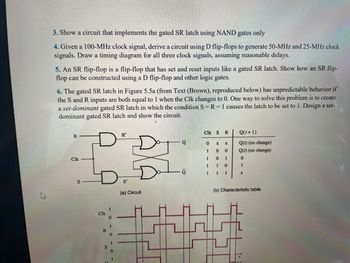

Transcribed Image Text:3. Show a circuit that implements the gated SR latch using NAND gates only

4. Given a 100-MHz clock signal, derive a circuit using D flip-flops to generate 50-MHz and 25-MHz clock

signals. Draw a timing diagram for all three clock signals, assuming reasonable delays.

5. An SR flip-flop is a flip-flop that has set and reset inputs like a gated SR latch. Show how an SR flip-

flop can be constructed using a D flip-flop and other logic gates.

6. The gated SR latch in Figure 5.5a (from Text (Brown), reproduced below) has unpredictable behavior if

the S and R inputs are both equal to 1 when the Clk changes to 0. One way to solve this problem is to create

a set-dominant gated SR latch in which the condition S = R = 1 causes the latch to be set to 1. Design a set-

dominant gated SR latch and show the circuit.

DT

R

Clk

S

Clk

R

0

R'

(a) Circuit

CIK S R

0

1

1

1

1

X

0

0

1

1

X

0

1

0

1

Q(1+1)

Q(1) (no change)

Q(1) (no change)

0

1

X

(b) Characteristic table

7:

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution

Trending nowThis is a popular solution!

Step by stepSolved in 3 steps with 3 images

Knowledge Booster

Similar questions

- The solutions provided didn't work for any of the questions. Please provide different solutions for the 3 questionsarrow_forwardTask 4: The InstantRide Finance team also wants to analyze travels where more than the average discount rate is applied. They want to look for any correlation between higher discount amounts against other travel characteristics. You need to create a SELECT statement which is filtered with a subquery to calculate the AVG of the TRAVEL_DISCOUNT column. Task: Find all travels where an above average discount was applied. (SQL Database Test)arrow_forwardPlease help with the following: Which column name is valid? Select one: a. NUMBER_1$ b. NUMBER c. 1_NUMBER# d. 1NUMBERarrow_forward

- What is the name of the columns of thee left hand side of the relationships between columns called?arrow_forwardBy default, data returned by the SQL SELECT statement is in descending order. a. True b. Falsearrow_forwardWhen used in a parameter query, which of the following WHERE clauses will select the records for employees working more than 40 hours? a. WHERE Hours > @Hours b. WHERE Hours > !Hours c. WHERE Hours > #Hours d. WHERE Hours > %Hoursarrow_forward

- Write a SELECT statement that uses the ranking functions to rank products by the total quantity sold. Return these columns: The product_name column from the Products table A column named total_quantity that shows the sum of the quantity for each product in the Order_Items table A column named rank that uses the RANK function to rank the total quantity in descending sequence A column named dense_rank that uses the DENSE_RANK function to rank the total quantity in descending sequencearrow_forwardwhere 'Where clause' used ?arrow_forwardwhen saying between 100 to 1000. Are 100 and 1000 included or not?arrow_forward

- The Colombia City office of StayWell indicated that there is a new tenant by the name of Yigit Yilmaz staying at the property with an ID of 13. You need to include this new resident in the RESIDENTS table.arrow_forwardWhich clause of a SQL Select statement is required if we want to display aggregate data by category such as total population by state, department, etc.? Question 40 options: 1) GROUP BY 2) ORDER BY 3) WHERE 4) FROM 5) SELECTarrow_forwardCreate a list of all number data types. SQLarrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY