Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN: 9780133594140

Author: James Kurose, Keith Ross

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

thumb_up100%

please explain and make sure the answer is correct

Question 2,3

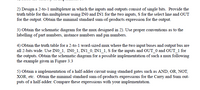

Transcribed Image Text:2) Design a 2-to-1 multiplexer in which the inputs and outputs consist of single bits. Provide the

truth table for this multiplexer using INO and IN1 for the two inputs, S for the select line and OUT

for the output. Obtain the minimal standard sum-of-products expression for the output.

3) Obtain the schematic diagram for the mux designed in 2). Use proper conventions as to the

labelling of part numbers, instance numbers and pin numbers.

4) Obtain the truth table for a 2-to-1 word-sized mux where the two input buses and output bus are

all 2-bits wide. Use INO_1, INO_1, IN1_0, IN1_1, S for the inputs and OUT_0 and OUT_1 for

the outputs. Obtain the schematic diagram for a possible implementation of such a mux following

the example given in Figure 3.3

5) Obtain a implementation of a half-adder circuit using standard gates such as AND, OR, NOT,

XOR, etc. Obtain the minimal standard sum-of-products expressions for the Carry and Sum out-

puts of a half-adder. Compare these expressions with your implementation.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 2 steps with 2 images

Knowledge Booster

Similar questions

- The following two SQL statements will produce the same results. SELECT P_DESCRIPT, P_QOH,P_PRICE FROM PRODUCT WHERE P_QOH >(SELECT P_QOH FROM PRODUCT WHERE P_CODE='11QER/31') AND P_PRICE>(SELECT P_PRICE FROM PRODUCT WHERE P_CODE='11QER/31'); SELECT P_DESCRIPT, P_QOH,P_PRICE FROM PRODUCT WHERE (P_QOH,P_PRICE) > (SELECT P_QOH,P_PRICE FROM PRODUCT WHERE P_CODE='11QER/31'); A) True B) Falsearrow_forwardNEED HELP WITH PYTHON CODE. ALSO, PLEASE PROVIDE DETAILS SEPARATELY ON HOW AND WHAT DID U USE TO GET UR CODE DONE.arrow_forward. Write a stored procedure named printOrderFreights(). The printOrderFreights()procedure should use cursor processing to find those orders whose freight is less than or equal to 0.2 and then print the “Freight is less than or equal to $0.2” message for each and every row that satisfies the condition. Hint: You need to use cursor processing for this stored procedure. Hint: Follow the 5 steps of cursor processing and declare any variables needed.arrow_forward

- This is a new homework assignment. Fill in the blanks.arrow_forwardTHis answer does not include line C2 or C3.arrow_forwardWhat is the Manhattan distance between different points as shown below? Fill the table with appropriate Manhattan distances. As an example, the distance between points A and C is computed in the appropriate table cellarrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON

Computer Networking: A Top-Down Approach (7th Edi...Computer EngineeringISBN:9780133594140Author:James Kurose, Keith RossPublisher:PEARSON Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science

Computer Organization and Design MIPS Edition, Fi...Computer EngineeringISBN:9780124077263Author:David A. Patterson, John L. HennessyPublisher:Elsevier Science Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning

Network+ Guide to Networks (MindTap Course List)Computer EngineeringISBN:9781337569330Author:Jill West, Tamara Dean, Jean AndrewsPublisher:Cengage Learning Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning

Concepts of Database ManagementComputer EngineeringISBN:9781337093422Author:Joy L. Starks, Philip J. Pratt, Mary Z. LastPublisher:Cengage Learning Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education

Prelude to ProgrammingComputer EngineeringISBN:9780133750423Author:VENIT, StewartPublisher:Pearson Education Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Sc Business Data Communications and Networking, T...Computer EngineeringISBN:9781119368830Author:FITZGERALDPublisher:WILEY

Computer Networking: A Top-Down Approach (7th Edi...

Computer Engineering

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:PEARSON

Computer Organization and Design MIPS Edition, Fi...

Computer Engineering

ISBN:9780124077263

Author:David A. Patterson, John L. Hennessy

Publisher:Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:9781337569330

Author:Jill West, Tamara Dean, Jean Andrews

Publisher:Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:9781337093422

Author:Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:9780133750423

Author:VENIT, Stewart

Publisher:Pearson Education

Sc Business Data Communications and Networking, T...

Computer Engineering

ISBN:9781119368830

Author:FITZGERALD

Publisher:WILEY