Database System Concepts

7th Edition

ISBN: 9780078022159

Author: Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher: McGraw-Hill Education

expand_more

expand_more

format_list_bulleted

Concept explainers

Question

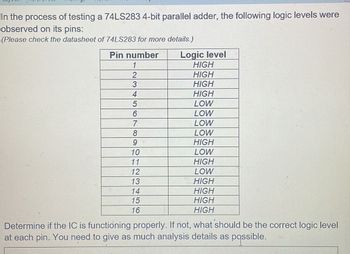

Transcribed Image Text:In the process of testing a 74LS283 4-bit parallel adder, the following logic levels were

observed on its pins:

(Please check the datasheet of 74LS283 for more details.)

Pin number

1

Logic level

HIGH

2

HIGH

3

HIGH

4

HIGH

5

LOW

6

LOW

7

LOW

8

LOW

9

HIGH

10

LOW

11

HIGH

12

LOW

13

HIGH

14

HIGH

15

HIGH

HIGH

16

Determine if the IC is functioning properly. If not, what should be the correct logic level

at each pin. You need to give as much analysis details as possible.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 3 steps with 7 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- Čreate a mechanism to detect when the output is decimal value '11' using 2 input logic gates.arrow_forwardThe timing diagram in Figure 8.99 shows the input waveforms of a NAND latch. Complete the diagram by showing the output waveforms. 8.7 Ans: (Note: you can plot the timing on the above figure.)arrow_forwardFor the 74ALS138 logic circuit shown in the figure below, answer the following questions: 1- Find the truth table of the 74ALS138 logic circuit. 2- Indicate the states of the 74ALS138 outputs for each of the following sets of inputs. a) E3 E21, E₁ = 0, A₂ = A₁ = 1, A₁ = 0 b) E3 = 1, E2= E₁ = 0, A₂ = 0, A₁ = A0 = 1 A2 A₁ Ao Ē₁ Ē₂ E3 299 74ALS138 1-of-8 decoder E 1407 06 05 04arrow_forward

- The data select inputs of 1 to 64 De-Muitiplexer is?arrow_forwardThe D flip-flop is created by connecting two gated D latches serially, and inverting the CLK input to one of them. The following figure shows the internal circuit of D Flip-flop composing of two latches (L1: Master, and L2: Slave) and NOT gate. Answers the following questions. (Note: You should show all the steps) Complete the truth table below. CLK D CLK1 N1 CLK2 Q Q' 0 0 1 0 0 1 1 1arrow_forwarda) Before designing the combinational circuit, you need to identify the pin configuration of the 7-segment diplay chip. Using the data book, write the pin configuration of the two 7- segment diplay chip. Pin # (top) Left to right Pin# (bottom) Left to right 1 2 123 466 7 8 9 3 4 8. el a lo 7 9. 9 1? 345 6 7 8 9arrow_forward

- Task 3: Use of 7-Segment Decoder IC a) Using the data book, label the pin configuration of the BCD to 7-segment decoder chip. For common anode, use 7448 İC and 7447 IC for common cathode. Pin Nos. 10 11 13 14 15 1|z3|| 45|||| 7 16 OH2 3456Darrow_forwardYou are requested to design 16 x 1 multiplexer, meaning that this combinational circuit has 16 data inputs and produces a single output using selection bits. How many selection bits require? Question 5 options: - 4 - 5 - 2 - 3arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education

Database System ConceptsComputer ScienceISBN:9780078022159Author:Abraham Silberschatz Professor, Henry F. Korth, S. SudarshanPublisher:McGraw-Hill Education Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON

Starting Out with Python (4th Edition)Computer ScienceISBN:9780134444321Author:Tony GaddisPublisher:PEARSON Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON

Digital Fundamentals (11th Edition)Computer ScienceISBN:9780132737968Author:Thomas L. FloydPublisher:PEARSON C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON

C How to Program (8th Edition)Computer ScienceISBN:9780133976892Author:Paul J. Deitel, Harvey DeitelPublisher:PEARSON Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning

Database Systems: Design, Implementation, & Manag...Computer ScienceISBN:9781337627900Author:Carlos Coronel, Steven MorrisPublisher:Cengage Learning Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersComputer ScienceISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Database System Concepts

Computer Science

ISBN:9780078022159

Author:Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:9780134444321

Author:Tony Gaddis

Publisher:PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:9780132737968

Author:Thomas L. Floyd

Publisher:PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:9780133976892

Author:Paul J. Deitel, Harvey Deitel

Publisher:PEARSON

Database Systems: Design, Implementation, & Manag...

Computer Science

ISBN:9781337627900

Author:Carlos Coronel, Steven Morris

Publisher:Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education