Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN: 9780133923605

Author: Robert L. Boylestad

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

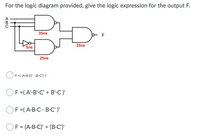

Transcribed Image Text:For the logic diagram provided, determine the logic expression for the output F.

### Logic Diagram

The diagram consists of three logic gates:

1. **AND Gate** (top left):

- Inputs: A, B, C

- Delay: 35 ns

2. **NOT Gate**:

- Input: B

- Output goes into the OR gate and another AND gate

- Delay: 5 ns

3. **AND Gate** (bottom):

- Inputs: B' (output from NOT gate), C

- Delay: 25 ns

4. **OR Gate** (center):

- Inputs: Outputs from the two AND gates

- Delay: 25 ns

- Output: F

### Logic Expression Options

- \( F = (A \cdot B \cdot C') \cdot (B \cdot C)' \)

- \( F = (A' \cdot B' \cdot C' + B' \cdot C)' \)

- \( F = (A \cdot B \cdot C \cdot B' \cdot C')' \)

- \( F = (A \cdot B \cdot C') + (B \cdot C')' \)

### Explanation

Select the correct logic expression based on the diagram and the listed options. The total delay is measured from the path with the greatest cumulative gate delay, which affects the timing performance of the circuit.

Expert Solution

arrow_forward

Step 1

Given the circuit diagram:

We need to find the logic expression for the output F.

Step by stepSolved in 2 steps with 2 images

Knowledge Booster

Similar questions

- Combinational Circuits - Design Procedure Design a logic circuit that has three inputs A, B, C and whose output will be HIGH only when a majority of the inputs are HIGH. 3-A. Generate the truth table. 2-B. Obtain the KMAP. 3-C. Provide the Simplified Boolean Function. 3-D. Generate the Logic diagram of the simplified Boolean function.arrow_forwardWhich boolean expression related to this combinational logic circuit? A B C D LONDR OY (A + B). (A + C) + B OY (A B) + (A. C). B OY (A B) + (A. C). B OY (A.B) + A.C + B OY (AB) + A. C + B OY= (A + B). (A+C) + B OY (AB) + A.C + B Yarrow_forwardWhich of the following statements accurately represents the best method of logic circuit simplification? a. Actual circuit trial and error evaluation and waveform analysis b. Boolean algebra and actual circuit trial and error evaluation c. Karnaugh mapping and circuit waveform analysis d. Karnaugh mapping and Boolean algebraarrow_forward

- Draw the logic circuit for each of the following Boolean expressions: Y=AB + BC b. Y=ACD + BCDarrow_forward2. Answer the questions about the ladder logic program shown below. Timer_1.DN TON Timer Preset Accum a.) At 23 seconds after the program is started, what are the following values? i. Timer_1.ACC ii. Counter_1.ACC b.) How many seconds after the program starts will PB1 turn on? Timer_1.DN 36 Counter_1.DN ㅋㅌ Timer 1 (EN) 5000 (DN) CTU Counter Counter_1 CU Preset (DN) Accum 8 04 PB1arrow_forwardQ18 Find the expression for the output of the logic circuits shown in Figure below. A DAD C B Farrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:9781337900348

Author:Stephen L. Herman

Publisher:Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:9780078028229

Author:Charles K Alexander, Matthew Sadiku

Publisher:McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:9780134746968

Author:James W. Nilsson, Susan Riedel

Publisher:PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:9780078028151

Author:Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:Mcgraw-hill Education,