Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN: 9780133923605

Author: Robert L. Boylestad

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Concept explainers

Question

Transcribed Image Text:HW 8.4 - Test Benches

Problem 8.4.4

Design a VHDL test bench to verify the functional operation of the system in the following figure using report and assert statements. Your test bench should drive in each input

code for the vector ABCD in the order they appear in the truth table (i.e., "0000", “O001", “0010", ...). Have your test bench change the input pattern every 10 ns using the wait for

statement within your stimulus process. Use the report and assert statements to output a message on the status of each test to the simulation transcript window. For each

input vector, create a message that indicates the current input vector being tested, the resulting output of your DUT, and whether the DUT output is correct.

NOTE: You will need to design the SystemJ.vhd system. Use a case statement to implement the logic.

SystemJ.vhd

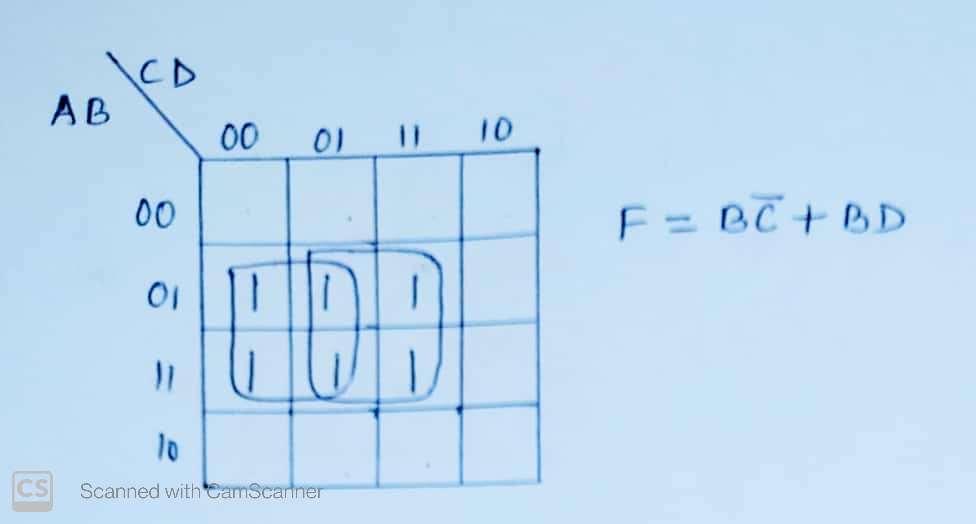

F = EAB.C.D(4,5,7,12,13,15)

4

HABCD

F

Deliverables: Simulate your model and test bench using ModelSim. You are to upload your VHDL test bench file (SystemJ_TB.vhd) and a screenshot of your report outputs in the

transcript portion of the ModelSim window (name it transcript_8_4_4.jpg) to the HW 8.4 Assignment Folder. Make sure to resize the transcript window so that I can tell if it is

working.

Expert Solution

arrow_forward

Step 1

Trending nowThis is a popular solution!

Step by stepSolved in 3 steps with 2 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Similar questions

- 3. Analyze the following design based on different values of X and Y and determine whether it can store a bit of information. If yes, form the characteristic table and show each of the set, reset, store, and complement actions if available. Otherwise, explain the problem with the design. DDarrow_forwardWrite, and test using spim, an assembly language program that inputs acharacter string from the user (you can assume that the string will be at most 20characters, not including the zero byte delimiter), forms a new string that contains thecharacters of the input string, but in reverse order, and then outputs the new string.arrow_forwardFind the Boolean expressions and use theorem 1.1.1 to show that the two circuits are equivalentarrow_forward

- Determine and graph the entropy (average information) of binary code in which the probability of occurrence of the two symbols is A and B. Then, find the entropy if probability of A = 0.8 using two methods: the equations and the graph.arrow_forwardHello, can someone help me with these two questions? Thank you!arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:9781337900348

Author:Stephen L. Herman

Publisher:Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:9780078028229

Author:Charles K Alexander, Matthew Sadiku

Publisher:McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:9780134746968

Author:James W. Nilsson, Susan Riedel

Publisher:PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:9780078028151

Author:Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:Mcgraw-hill Education,