Obtain the waveform of output states Q and for the D latch when the input condition as in Figure 5 is given ( explain your result )

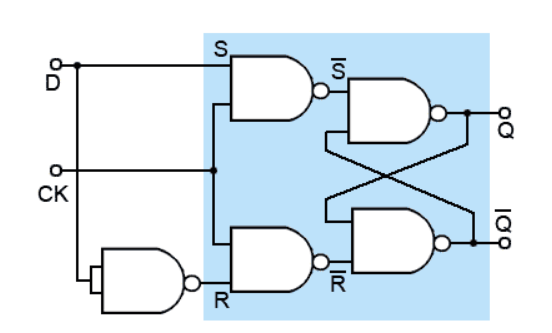

D Flip Flop : It is the very important type of flip flop which ensures that both S and R input of SR flip flop will never gives 1 as output which is the major drawback of SR flip flop. D stands for Delay.

Operation : D flip flop will have two inputs signal - one is the clock other is the actual input. When clock signal is 0 then output will be same as the previous output no change in the data. But when clock signal is high then output will change according to the input.

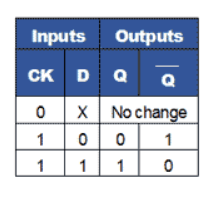

Below attached is the table to show the working functionality of D flip flop:

CK is the clock signal.

D flip flop Diagram :

Step by step

Solved in 2 steps with 3 images