Oh no! Our experts couldn't answer your question.

Don't worry! We won't leave you hanging. Plus, we're giving you back one question for the inconvenience.

Submit your question and receive a step-by-step explanation from our experts in as fast as 30 minutes.

You have no more questions left.

Message from our expert:

Our experts are unable to provide you with a solution at this time. Try rewording your question, and make sure to submit one question at a time. We've credited a question to your account.

Your Question:

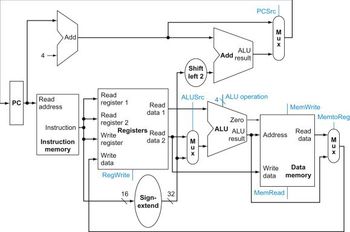

Assume that individual stages of the datapath have the following latencies:

- IF: 250ps

- ID: 350ps

- EX: 150ps

- MEM: 300ps

- WB: 200ps

-

- List the required stages for each of the following types of instructions: load, store, r-type, branch.

- What is the execution time of each type of instruction assuming only the required stages execute for each instruction?

- Assuming the same instruction mix listed in Problem 7, what is the average execution time across all instructions?

- Assuming pipelining is used, what would be the necessary clock cycle time?

- Assuming pipelining is used, what would be the execution time for a single load instruction to execute?

- Use the average instruction execution time calculated in Part d of this problem to determine the overall speed-up gained by pipelining. Assume the processor continuously runs with a full pipeline and hazards are completely avoided.

Transcribed Image Text:PC

Read

address

Add

Instruction

Instruction

memory

Read

register 1

Read

register 2

Registers Read

data 2

Write

register

Write

data

RegWrite

Read

data 1

16

Sign-

extend

32

Shift

left 2

ALUSrc

E3X

Add

ALU

result

ALU operation

Zero

ALU ALU

PCSrc

result

Address

MemWrite

MemRead

Read

data

Write Data

data

memory

MemtoReg

MUX

Want to see the full answer?

Check out a sample Q&A hereKnowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Similar questions

- In the context of access control, what is the difference between a subject and an object?arrow_forwardIs it possible for the income statement and balance sheet columns of a worksheet to total when they are first added?arrow_forwardLanguage: Python————————————————— The data:A ={ "action": [ { "logType": “123x43” }, { "logType": “123x43” }, { "logType": “2y4y5y” }, { "logType": “123x43” }, { "logType": “2y4y5y” }, { "logType": “6z4zz” }, { "logType": “2y4y5y” }, { "logType": “123x43” }, { "logType": “2y4y5y” }, { "logType": “6z4zz” }}———————————————————————— A desire output:{ “123x43”: 4, “2y4y5y”: 4, “6z4zz”: 2} How could I make the above result …?arrow_forward

- The Little Man Computer Calculator Mailboxes 00 500 01 199 02 500 03 399 In Basket 95 96 97 98 99 123 Out Basket 05 Little man Instruction location counter Reset button 1. The Out instruction copies data from the a. In basket to a mailbox alculator to a mailbox c. In basket to the calculator d. mailbox to the calculator e. calculator to the In basket f. none of the abovearrow_forwardComputer Science Assume you are a software developer that has written a system that analyses pictures of various recyclable items (such as a can, bottle or a crate). It can be used via a Web Application (Web API), i.e., the users send pictures over the Internet. The system returns for each picture how many of each item are seen in the picture. Discuss if this service should be offered for free. Justify your answerarrow_forwardvisits Patiend- D physician- p Doctoon Or dered Testo Phy sian-ID Physian-ID patiend -ID Name Time Speciality Test-ID Degree ličense number Reason vitals patients Tests CPT-Co des vital -1D Test -ID Patient-ID CPT-Code Height weight Tempenatune pulse Ratt Blood presure Name SSN Datt -ordned Date -Retund Resutt Name Description DOB PHONE PRIMARY phys/ciaD Evends Event-Types Patient ID vit al - Datt vital -Time Event- ID Patient-ID Event -Code Code conditions Stont -Datl Diagnosis patient - ID phy sian - ID Con dition Daity ICDIO END - Datl Name Description Based upon the above schema: For each of the following, indicate whether the described result is a slice, a dice, a rollup, or a drilldown: An administrative worker uses the data warehouse to investigate survey scores based on patients that saw physicians with 3 specialities during the period 2017- 2018 after being diagnosed with conditions relating to lung disease. An administrative worker views results only for a particular…arrow_forward

- Write a Python Program to perform file operations such as open read, write and close on text and numeric data files with examples.arrow_forwardPep/9 Simulator Example Program D1 FC 15 F1 00 18 C1 00 17 61 00 15 E1 00 17 D1 00 18 F1 FC 16 00 01 zz What does it do???????arrow_forwardPlease please please don't copy Computer Science Q1: Antony Tang, an architect and one of the reviewers of this book, says that he has used a development view—a kind of quality view—that describes how the software should be developed in relation to the use of tools and development workflows, the use of standard library routines such as for exception handling, some coding conventions and standards, and some testing and deployment conventions. Sketch a definition of a development view. please i need as short answer as possible with justificationarrow_forward

- 2) After a data-mining course the results of the exam was recorded along with some data about the students. The results can be found in in the table below. (GPA is the Grade Point Average.) ID Phone number Language Passed all assignments GPA Passed exam 555 - 3452 555 - 6294 1 Java No 3.1 Yes Java No 2.0 No 3 555 - 9385 C++ Yes 3.5 Yes 4 555 - 9387 Python Yes 2.5 Yes 555 - 9284 555 - 0293 555 - 9237 555 - 3737 Java Yes 3.9 No C++ No 2.9 No 7 Java No 1.9 No 8 Python Yes 3.2 Yes In no more than one page of text, describe the design of a K-Nearest Neighbor classifier to predict which student will fail or pass the exam. b. Use your K-NN classifier to predict if the following student (who has slept too much and missed the main test) will succeed in the retest. а. ID Phone number Language Passed all assignments GPA Passed exam Yes 555 - 6295 C++ 3.0 ?arrow_forwardGive proper explaination of incorrect and correct answer A program can alter it's behaviour dynamically in several different ways. Which of the following is not one of ways ? a. Changes its metadata directly b. Intercede in its execution c. Use the metadata d. Delete the metdataarrow_forwardUse object-oriented design to design a class called Rectangle that will receive thelength and breadth of a rectangle, validate the input data and calculate and displaythe area of the rectangle.a Design the class table.b Write an algorithm for each operation.c Write a test or driver algorithm to test the solution. Simple Program and Design a step by step Appraoch 5th edition ISBN 1423901320arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning

Systems ArchitectureComputer ScienceISBN:9781305080195Author:Stephen D. BurdPublisher:Cengage Learning Microsoft Visual C#Computer ScienceISBN:9781337102100Author:Joyce, Farrell.Publisher:Cengage Learning,

Microsoft Visual C#Computer ScienceISBN:9781337102100Author:Joyce, Farrell.Publisher:Cengage Learning, Fundamentals of Information SystemsComputer ScienceISBN:9781305082168Author:Ralph Stair, George ReynoldsPublisher:Cengage Learning

Fundamentals of Information SystemsComputer ScienceISBN:9781305082168Author:Ralph Stair, George ReynoldsPublisher:Cengage Learning- Programming Logic & Design ComprehensiveComputer ScienceISBN:9781337669405Author:FARRELLPublisher:Cengage

Systems Architecture

Computer Science

ISBN:9781305080195

Author:Stephen D. Burd

Publisher:Cengage Learning

Microsoft Visual C#

Computer Science

ISBN:9781337102100

Author:Joyce, Farrell.

Publisher:Cengage Learning,

Fundamentals of Information Systems

Computer Science

ISBN:9781305082168

Author:Ralph Stair, George Reynolds

Publisher:Cengage Learning

Programming Logic & Design Comprehensive

Computer Science

ISBN:9781337669405

Author:FARRELL

Publisher:Cengage