Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN: 9780133923605

Author: Robert L. Boylestad

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

Need a sol

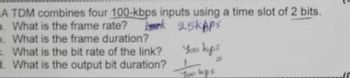

Transcribed Image Text:A TDM combines four 100-kbps inputs using a time slot of 2 bits.

a. What is the frame rate? k 95kbps

b. What is the frame duration?

What is the bit rate of the link?

d. What is the output bit duration?

You hops

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 2 steps

Knowledge Booster

Similar questions

- 2. According to the following figure, the LED of a 7-segment decoder (Inset) will display a "0" when VI1, VI2...VI7 are in what bit sequence? V12 Ipi 10² 1 Iptarrow_forwarda) i) Determine the number of bits per level required when using FSK with 4 different frequencies and QAM with a constellation of 256 points. ii) We want to digitise a signal that contains frequencies between 100 Hz and 1500 Hz, assuming 16 bits per sample. The digitised signal will be transmitted using a QPSK process. Determine the bit rate and the level rate. iii) We need to send 210,000 bits per second over a noiseless channel using 128- QAM. Determine the required bandwidth.arrow_forwardA digital signaling system is required to operate at 9600 bps. a. If a signal element encodes a 4-bit word, what is the minimum required band-width of the channel? b. Repeat part (a) for the case of 8-bit words.arrow_forward

- We can Design ripple counter that counts from 0 to 10 by inserting (A3,A1) to NAND gate and connect the output of the NAND gate to _____ input, where as the data input is 0000arrow_forward23. Determine the step size for a 4-bit ADC having a range of 10V. Also, convert an analog sample of 3V into the 4-bit digits using Successive approximation method. Please show all steps/comparisons/SAR comparison rules used for each step to obtain full points.arrow_forwardGiven the positive number 77. a) Represent the number as an eight–bit number in two’s–complement form. Also give the 2 character hexadecimal value. b) Represent the negative number –77 as an eight–bit number in two’s–complement form. Also give the 2 character hexadecimal value. c) Add the binary result for a to b to verify you get an eight-bit value of zero!arrow_forward

- The state diagram of a sequence which allows overlap is shown below. A sequence detector accepts input a string of bits:either 0 or 1. Its output goes to 1 when a target sequence has been detected. In a sequence detector that allows overlap, the final bits of one sequence can be the start of another sequence. Using the state diagram given below and an input sequence 10110: A) Assign binary values to the states and derice the state table. B)derive the simplified state equations. c) Use JK flip-flop abd design a synchronous sequence detector circut. D) Is this Mealy or Moore model? Treat unused states as do not care conditionsarrow_forwardDesign a 6-bit ripple carry adder. Experimentally find out the sum of 110011 and 111001. Construct your entire schematic diagram and label all necessary pins and simulate for results.arrow_forward(a) Determine the worst-case delay of a 16-bit carry select adder. Assume tsetup = tsum = 2, and tcarry = tmux = 1. Compare this with the worst-case delay of a 16-bit ripple carry adder. (b) If each stage has 4 bits, what is minimum number of bits (N) do we need to have, in order for the carry-select adder to start showing less delay (when compared to a ripple-carry adder)? Assume tsetup = tsum = 2, and tcarry = tmux = 1.arrow_forward

- V DD V DD Figure 3 d M6 M2 CLK –|M4 CLK - |Mg D CLK –|M3 CLK H|M, Qs M1 M5 (c) Figure 3 shows the master and slave latch with an inverter in between. For the data input D and the clock signal CLK, draw the corresponding outputs Qm and Qs. Assume that CLK and CLK have an overlap. 0.4 0.2 timelsec) in)arrow_forwardTwenty two sources, four with a bit rate of 400 Mbps, ten with a bit rate of 200 Mbpsand eight with a bit rate of 100 Mbps are to be combined using TDM. If the unit size is20 bits determine the following questions:i. How this can be achieved?ii. Input time slotiii. Frame Sizeiv. Output time slotarrow_forwardQ1- Design a sequence generator to generate the sequence pattern (11001) using JK flip-flops and NAND gate only. Q2: Design 4-bit Parallel-in to Parallel-out (PIPO) using RS-F/F. Draw the parallel output waveform for the parallel inputs [1100,0101, 0001, 1010, 0111]. Then draw the state diagram.arrow_forward

arrow_back_ios

SEE MORE QUESTIONS

arrow_forward_ios

Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:9781337900348

Author:Stephen L. Herman

Publisher:Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:9780078028229

Author:Charles K Alexander, Matthew Sadiku

Publisher:McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:9780134746968

Author:James W. Nilsson, Susan Riedel

Publisher:PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:9780078028151

Author:Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:Mcgraw-hill Education,