Introductory Circuit Analysis (13th Edition)

13th Edition

ISBN: 9780133923605

Author: Robert L. Boylestad

Publisher: PEARSON

expand_more

expand_more

format_list_bulleted

Question

Please answer this question with as much details possible, so I can understand.

This is for Electrical Engineering.

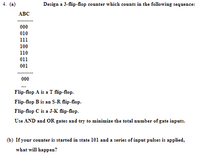

Transcribed Image Text:4. (a)

Design a 3-flip-flop counter which counts in the following sequence:

АВС

000

010

111

100

110

011

001

000

Flp-foр A is a T flip-Пор.

Flip-flop B is an S-R flip-flop.

Flip-flop C is a J-K flip-flop.

Use AND and OR gates and try to minimize the total number of gate inputs.

(b) If your counter is started in state 101 and a series of input pulses is applied,

what will happen?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 3 steps with 2 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Similar questions

- Module 10 Section Review 3.0.0.png Additional Resources Electronics Fundamentals: Circuits, Devices, and Applications, Principles of Electric Circuits, Thomas L. Floyd. New York: Prent 3.0.0 Section Review 1. The letter designation SL on an electrical draw- ing indicates a 4. A a. a. limit switch b. low-voltage switch c. load switch d. light switch b. C. d. 2. Existing power lines on an electrical site plan may be indicated by the letter 5. In t safe a. E b. I a. b. 2 С. Р d. V C. 2 d. 2: 3. The specific types of luminaires required in an installation can be found on the a. power plan b. electrical site plan c. schematic diagram d. lighting fixture schedule P Search for anythingarrow_forwardQuestion 5 What is the device address used by the instruction OUT A4, AL?arrow_forwardIn a range, signals may have an endless number of values.a. Analog b. Digital c. Either (a) or (b) d. None of the abovearrow_forward

- 1-What phrase is used when a substitution is permitted for a specific item? 2-The specifications state that all work shall be done... 3-What phrase is used when a substitution is permitted for a specific item? 4-What is the purpose of an electrical symbol? 5. Where are notations found?arrow_forwardPlease do a detail Compare and contrast of Power Drill vs Measuring Tapearrow_forwardHow is induction applied? For each , give details of how induction is achieved?arrow_forward

arrow_back_ios

arrow_forward_ios

Recommended textbooks for you

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON

Introductory Circuit Analysis (13th Edition)Electrical EngineeringISBN:9780133923605Author:Robert L. BoylestadPublisher:PEARSON Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning

Delmar's Standard Textbook Of ElectricityElectrical EngineeringISBN:9781337900348Author:Stephen L. HermanPublisher:Cengage Learning Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education

Programmable Logic ControllersElectrical EngineeringISBN:9780073373843Author:Frank D. PetruzellaPublisher:McGraw-Hill Education Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education

Fundamentals of Electric CircuitsElectrical EngineeringISBN:9780078028229Author:Charles K Alexander, Matthew SadikuPublisher:McGraw-Hill Education Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON

Electric Circuits. (11th Edition)Electrical EngineeringISBN:9780134746968Author:James W. Nilsson, Susan RiedelPublisher:PEARSON Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Engineering ElectromagneticsElectrical EngineeringISBN:9780078028151Author:Hayt, William H. (william Hart), Jr, BUCK, John A.Publisher:Mcgraw-hill Education,

Introductory Circuit Analysis (13th Edition)

Electrical Engineering

ISBN:9780133923605

Author:Robert L. Boylestad

Publisher:PEARSON

Delmar's Standard Textbook Of Electricity

Electrical Engineering

ISBN:9781337900348

Author:Stephen L. Herman

Publisher:Cengage Learning

Programmable Logic Controllers

Electrical Engineering

ISBN:9780073373843

Author:Frank D. Petruzella

Publisher:McGraw-Hill Education

Fundamentals of Electric Circuits

Electrical Engineering

ISBN:9780078028229

Author:Charles K Alexander, Matthew Sadiku

Publisher:McGraw-Hill Education

Electric Circuits. (11th Edition)

Electrical Engineering

ISBN:9780134746968

Author:James W. Nilsson, Susan Riedel

Publisher:PEARSON

Engineering Electromagnetics

Electrical Engineering

ISBN:9780078028151

Author:Hayt, William H. (william Hart), Jr, BUCK, John A.

Publisher:Mcgraw-hill Education,